#### Introduction to EFM32 API

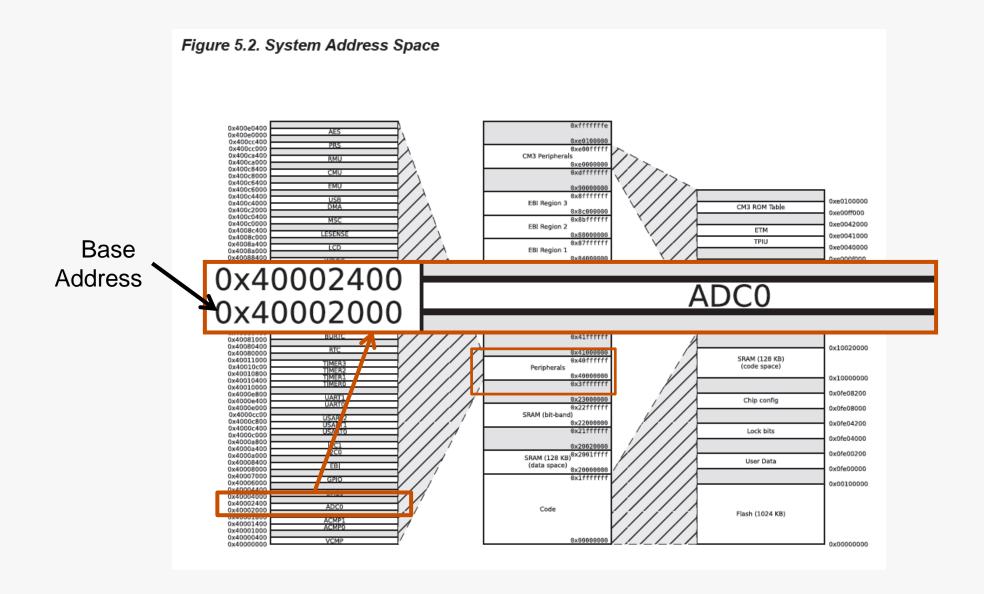

### Memory Mapped Peripherals

## Peripheral Registers

| Offset | Name             | Туре | Description                                 |

|--------|------------------|------|---------------------------------------------|

| 0x000  | ADCn_CTRL        | RW   | Control Register                            |

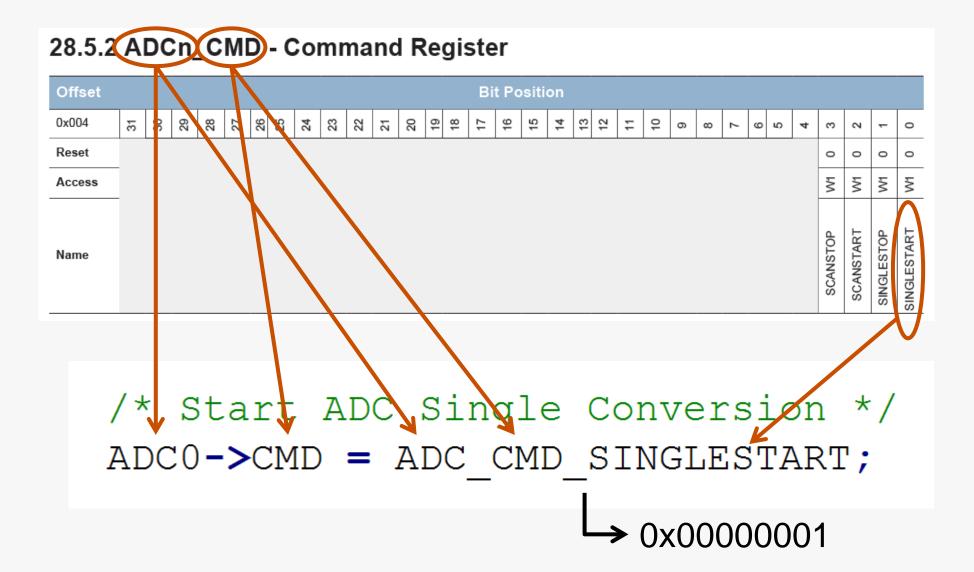

| 0x004  | ADCn_CMD         | W1   | Command Register                            |

| 0x008  | ADCn_STATUS      | R    | Status Register                             |

| 0x00C  | ADCn_SINGLECTRL  | RW   | Single Sample Control Register              |

| 0x010  | ADCn_SCANCTRL    | RW   | Scan Control Register                       |

| 0x014  | ADCn_IEN         | RW   | Interrupt Enable Register                   |

| 0x018  | ADCn_IF          | R    | Interrupt Flag Register                     |

| 0x01C  | ADCn_IFS         | W1   | Interrupt Flag Set Register                 |

| 0x020  | ADCn_IFC         | W1   | Interrupt Flag Clear Register               |

| 0x024  | ADCn_SINGLEDATA  | R    | Single Conversion Result Data               |

| 0x028  | ADCn_SCANDATA    | R    | Scan Conversion Result Data                 |

| 0x02C  | ADCn_SINGLEDATAP | R    | Single Conversion Result Data Peek Register |

| 0x030  | ADCn_SCANDATAP   | R    | Scan Sequence Result Data Peek Register     |

| 0x034  | ADCn_CAL         | RW   | Calibration Register                        |

| 0x03C  | ADCn_BIASPROG    | RW   | Bias Programming Register                   |

#### CMSIS Struct

```

typedef struct

__IO uint32_t CTRL; /**< Control Register */

IO uint32 t CNT; /**< Counter Value Register */

IO uint32 t COMP0; /**< Compare Value Register 0 */

IO uint32 t COMP1; /**< Compare Value Register 1 */

I uint32 t IF; /**< Interrupt Flag Register */

__IO uint32_t IFS; /**< Interrupt Flag Set Register */

IO uint32 t IFC; /**< Interrupt Flag Clear Register */

IO uint32 t IEN; /**< Interrupt Enable Register */

IO uint32 t FREEZE; /**< Freeze Register */

I uint32 t SYNCBUSY; /**< Synchronization Busy Register */

```

#### Read and Write Registers

```

/* Set compare value */

RTC->COMP0 = 42;

/* Read current counter value */

countValue = RTC->CNT;

```

#### **CMSIS Naming Convention**

7

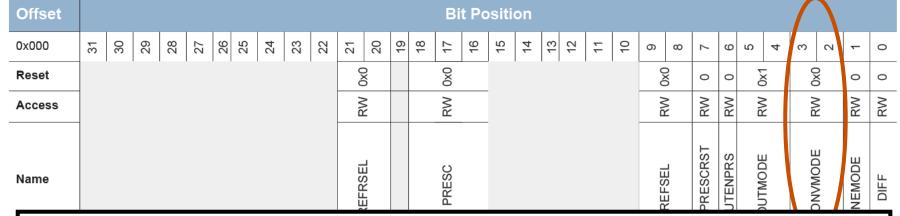

#### Set and Clear Bits

```

/* Set bit DIFF in DACO_CTRL */

DACO->CTRL |= DAC_CTRL_DIFF;

/* Clear bit DIFF in DACO_CTRL */

DACO->CTRL &= ~DAC_CTRL_DIFF;

```

#### Multiple-Bit Fields

# 29.5.1 DACn\_CTRL - Control Register

/\* Set sample-and-hold conversion mode \*/

DACO->CTRL = (DACO->CTRL & ^\_DAC\_CTRL\_CONVMODE\_MASK)

| DAC\_CTRL\_CONVMODE\_SAMPLEHOLD;

#### Configure conversion mode.

| Value | Mode       | Description                        |

|-------|------------|------------------------------------|

| 0     | CONTINUOUS | DAC is set in continuous mode      |

| 1     | SAMPLEHOLD | DAC is set in sample/hold mode     |

| 2     | SAMPLEOFF  | DAC is set in sample/shut off mode |

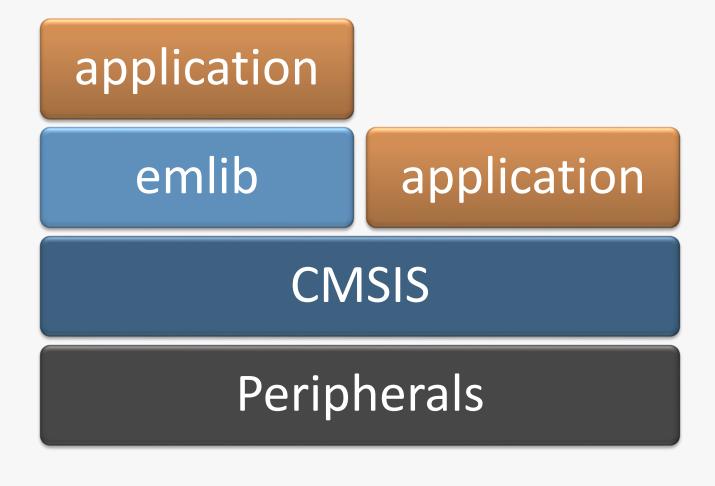

#### emlib

```

/* Init for single conversion use,

measure VDD/3 with 1.25 reference. */

ADC InitSingle TypeDef singleInit

= ADC INITSINGLE DEFAULT;

singleInit.reference = adcRef1V25;

singleInit.input = adcSingleInpVDDDiv3;

singleInit.resolution = adcRes12Bit;

singleInit.acqTime = adcAcqTime32;

ADC InitSingle (ADC0, &singleInit);

```

www.silabs.com/mcu